前回は、JK フリップフロップを使った 4進同期カウンタを設計してみました。

あちこちサイトをみていると、3進だ 5進だ n進だと、いろいろでてきます。でもまぁ、どれも考え方は同じなわけで、必要になったら考えればよいかな、と。

で、4進カウンタは 2ビットだったので、今回は、3ビットの同期カウンタを作ってみようと思います。3ビットなので、0b000 から 0b111 まで、8進数をアップ・カウントさせます。

JK フリップフロップを使った 8進同期カウンタ

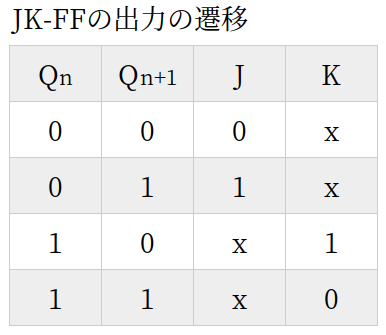

図1 は、JKフリップフロップの出力の遷移を表したものです。これ、すべてに必要な表なので、もう、覚えちゃいましょ (^_^;)

おさらいします。

Q が 0 で変化しないとき、J=0

Q が 0 → 1 になるとき、J=1

Q が 1 → 0 になるとき、K=1

Q が 1 で変化しないとき、K=0

JKフリップフロップの出力遷移をもとに作った真理値表が、図2 です。表が大きくなっていますが、各ビットごとの出力遷移と、そのビットの J、K の値に注目です。

たとえば、ビット 2。Q2(n) → Q2(n+1) が 0 → 0 ならば、J2=0、K2=x になる。

ビット 0 ならば、Q0(n) → Q0(n+1) が 0 → 1 なので、J0=1、K0=xになる。

こうして、すべての場合の J、K の値を埋めれば、真理値表のできあがり。

ちなみに、Q列の埋め方だけど。

たとえば、ビット 2 の列 (Q2(n)) の場合、22 = 4 だから、上から順に 0 が 4 個、1 が 4 個の繰返し。ビット 1 (Q1(n)) なら、21 = 2 だから、上から順に 0 が 2 個、1 が 2 個、と埋める。ビット 0 は 0 と 1 が交互に入る。バイナリコードを埋め込む手順な。

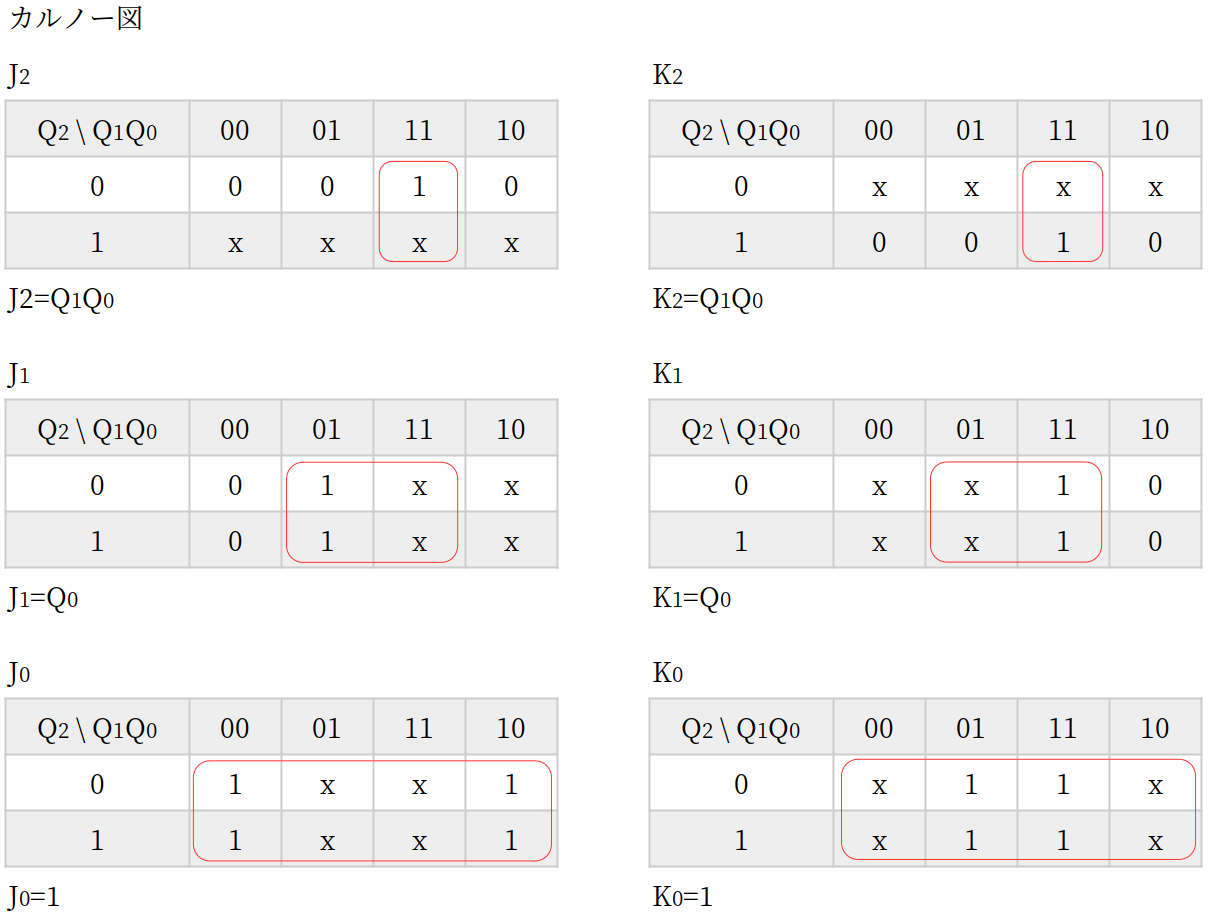

そして、すべての J、K に対してカルノー図をつくる。

ちなみに、赤枠は 2n 個、つまり 2、4、8、16、… 個の 1 をくくるんだよ。don’t care は 1 でも 0 でもいいんだから、つごうのいいように決める。上のカルノー図の場合、赤枠でくくっている中の x は 1、外の x は 0 ってことにしているわけだ。

で、論理式を求める。

たとえば J1 の場合。Q2 は 0 も 1 もあるので除外、Q1 も 0 も 1 もあるので除外。Q0 は 1 のみなので、J1=Q0 になる。

J0 = 1 K0 = 1 J1 = Q0 K1 = Q0 J2 = Q1・Q0 K2 = Q1・Q0

カルノー図に関しては、多くのグーグル先生が解説してくれているし、演習問題もいっぱいあるから、すぐに使えるようになりますよ。俺みたいに (^_^;)

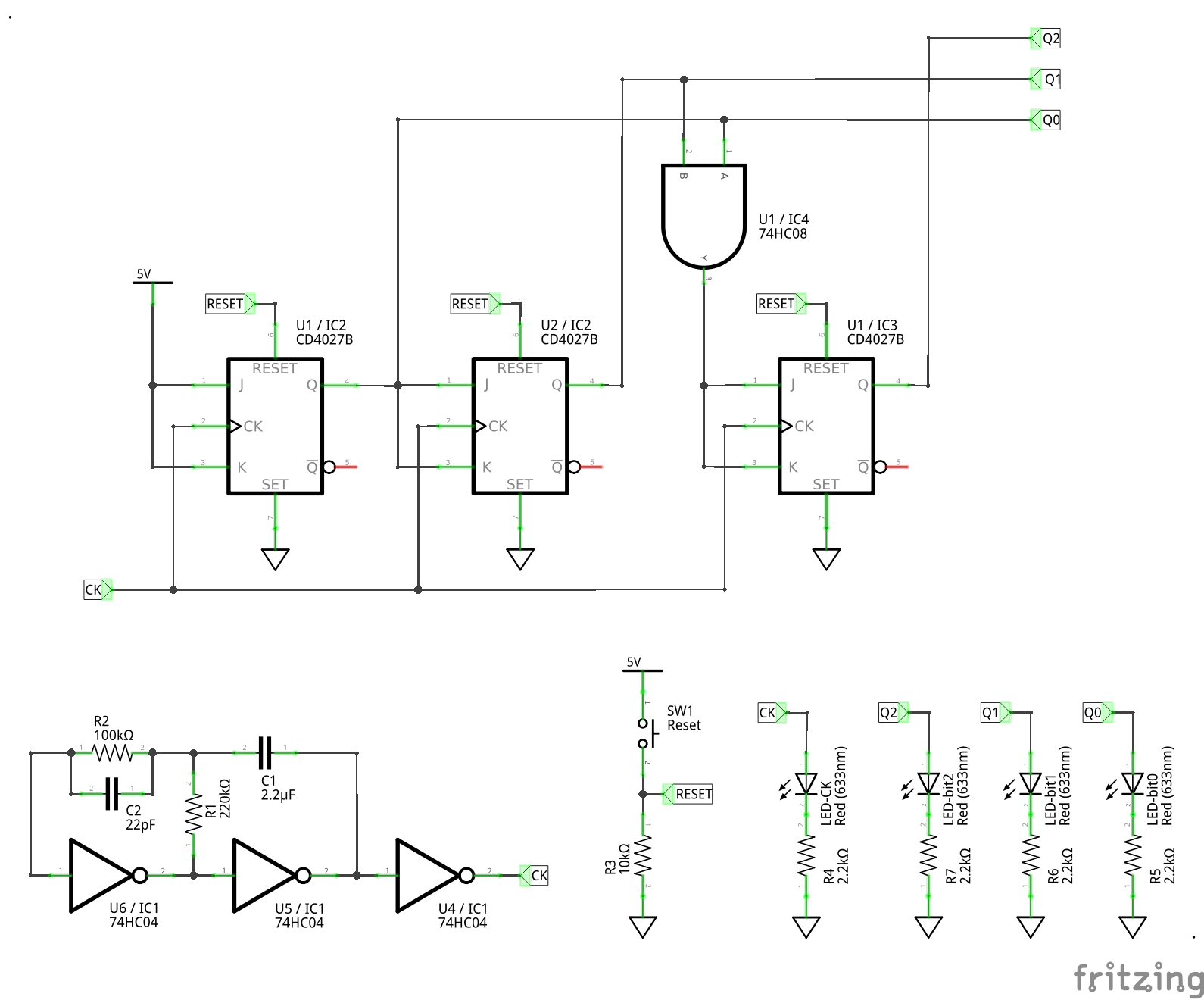

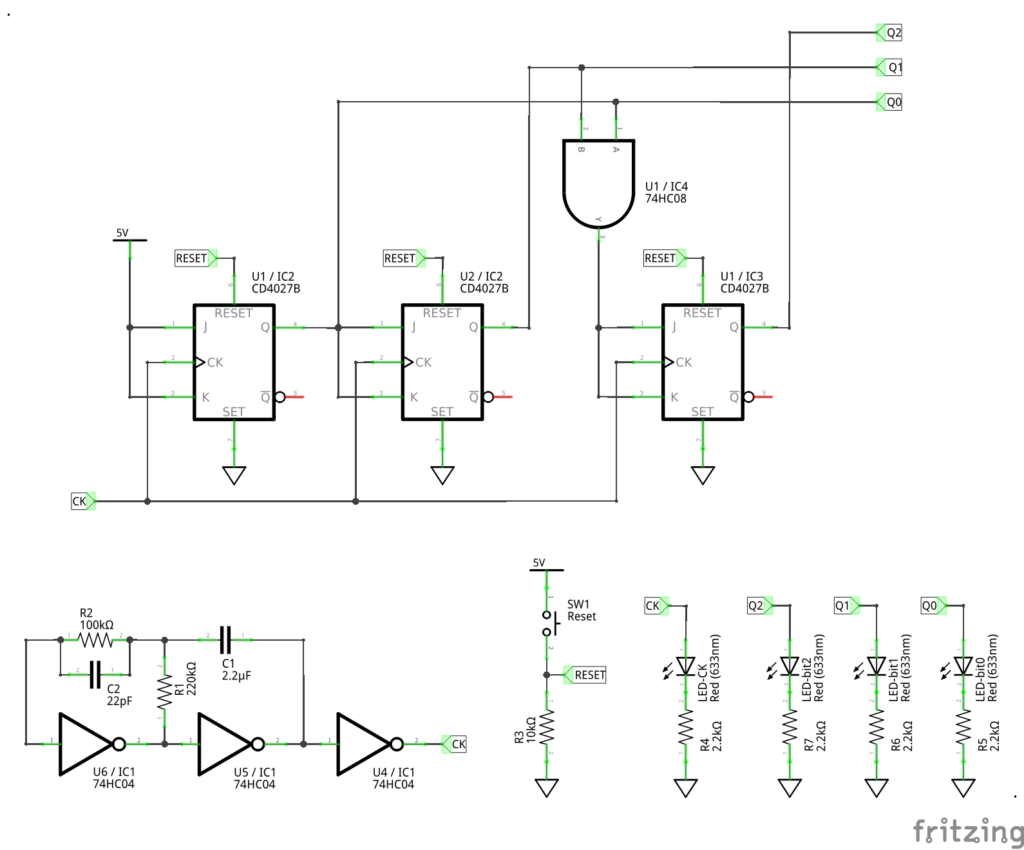

論理式ができたので、回路図を描きましょう。

カウンタ部分。

ビット 0 (U1/IC2) は、J0、K0 ともに 1 なので、Vcc につなぐ。

ビット 1 (U2/IC2) は、J1、K1 ともに Q0 なので、ビット 0 の出力 Q0 につなぐ。

ビット 2 (U1/IC3) は、J2、K2 ともに Q1・Q0 、つまり、Q1 と Q0 を AND して入力する。

左下はクロック発振回路。右下は、リセットスイッチ、クロック表示 LED と 3 ビットの出力表示 LED。これらは、これまでの回路と同じです。

ということで、AND ゲートを 1 個追加して、8進同期カウンタができました。

後記

ちなみに、AND に換えて、NOR ゲートを使って Q を入力してもいい。負理論入力の NOR は、AND と同じだから。また、出力表示 LED を Q につなぐと、ダウン・カウンタになる。真理値表の Q を反転させてみると、わかります。

俺はまだまだ未熟で自由に操れないけれど、ちょっと視点を変えることで、こうした論理回路はいろいろに変化する、んだそうだ。やっぱり論理だけじゃなくて、経験とか感性とか、必要なんだろうなぁ。

論理回路 / 基本的な論理回路

論理回路 / RSフリップフロップ

論理回路 / ゲート型 RS フリップフロップ

論理回路 / プライマリ・レプリカ型 RS フリップフロップ

論理回路 / Dフリップフロップ

論理回路 / JK フリップフロップ

論理回路 / 分周回路・カウンタ回路

論理回路 / 4進同期カウンタ (2bit)

論理回路 / 8進同期カウンタ (3bit)

論理回路 / 16進同期カウンタ (4bit)

論理回路 / 10進同期カウンタと 7セグメントLED

論理回路 / 半加算器と全加算器

論理回路 / 4ビット加算器の構成とシミュレーション

論理回路 / 4ビット加算器をロジック IC でつくる

加算器でカウンタを作る / 構成とシミュレーション

加算器でカウンタを作る / 16進カウンタ

加算器でカウンタをつくる / 10進カウンタ

論理回路 / シフトレジスタ・ジョンソンカウンタ・リングカウンタ

さらに…