前回は、半加算器、全加算器のおさらいと、動作のシミュレーションを行ないました。

1 ビットの加算をしてみたところで意味ないし、つまんないので、今回は 4 ビット加算器をつくってみましょう。まぁそれでも 30 まで (*) しか加算できない (;´Д`)

4 ビット桁上げ伝播加算器 (Ripple Carry Adder)

今回つくってみようとしている加算器は、「桁上げ伝播加算器 (Ripple Carry Adder)」というそうです。略して RCA。ケーブルでもレコードでもない、ない。

加算器は、下位桁の演算を行なって桁上げが決定されないと上位桁の演算ができない。なので、桁数が増えると演算時間が長くなる。

何桁ぐらいまでが使いものになるのかわからんです。つらつらググってみても、多ビット加算器をじっさいにつくってみた、なんていう記事があまり見つからないので、実用性にはとぼしいのかなぁ。

ちなみに、演算速度をあげる方法として、「桁上げ先見加算器 (Carry Look-ahead Adder)」とか「桁上げ選択加算器 (Carry Select Adder)」とか、あるんだとか。そのあたりはまた、気が向いたら。

4 ビット加算器の構成

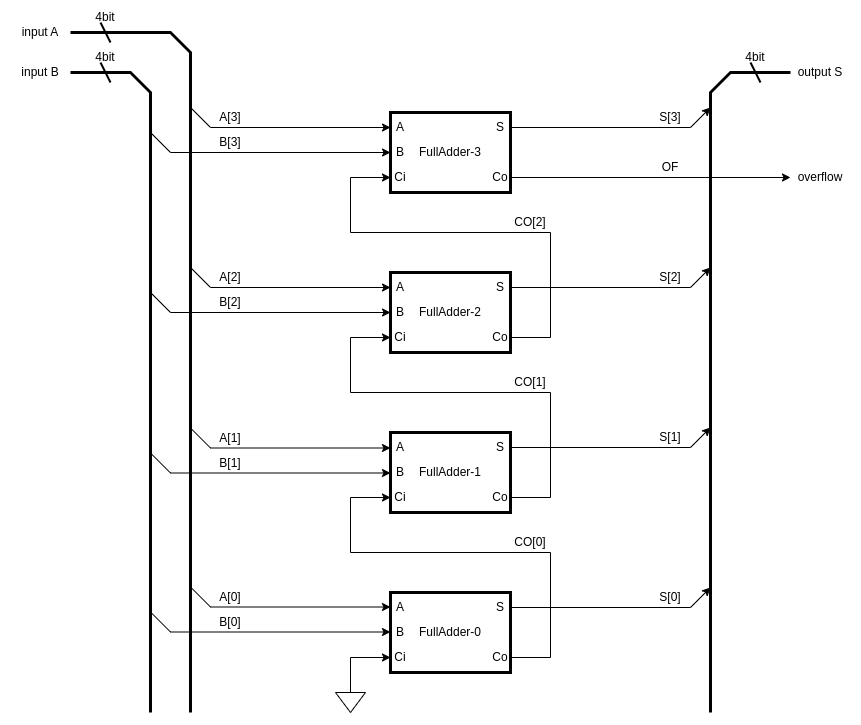

図 1 が、製作する 4 ビット加算器の構成ブロック図です。

加算器は、前回つくった全加算器を 4 個つかいます。

教科書的には、最下桁 bit0 は半加算器でよい。ですが、同じ回路を組んでパーツとしてつかうので、すべて全加算器としています。bit0 の Ci は 0 とします。

入力は 2 つの 4 ビットデータ A、B。出力は 4 ビット S。

最上桁のキャリーはオーバーフロー OF としますが、出力を 5 ビットと考えることもできます。そのあたりは、用途次第。

4 ビット加算器のシミュレーション

シミュレーションする必要性はあまりないのですが、お勉強です。VerilogHDL でシミュレーションしてみましょう。新しい記述もでてきます。

VerilogHDL 回路記述

前回、全加算器のシミュレーションをやりましたので、そのモジュールをそのまま利用しましょう。全加算器の回路記述は、前回記事を参照して下さい。

- module ADDER_4BIT(

- input wire [3:0] A, B,

- output wire [3:0] S,

- output wire OF

- );

- wire CO [0:2];

- FULL_ADDER FA0(.A(A[0]), .B(B[0]), .CI(1'b0), .S(S[0]), .CO(CO[0]));

- FULL_ADDER FA1(.A(A[1]), .B(B[1]), .CI(CO[0]), .S(S[1]), .CO(CO[1]));

- FULL_ADDER FA2(.A(A[2]), .B(B[2]), .CI(CO[1]), .S(S[2]), .CO(CO[2]));

- FULL_ADDER FA3(.A(A[3]), .B(B[3]), .CI(CO[2]), .S(S[3]), .CO(OF));

- endmodule

7 行目は内部信号 CO のワイヤ宣言ですが、いわゆる配列です。3 個の要素を宣言しています。ちなみに、二次元配列も可能、らしい。

入力 A などは、4 ビット幅として [3:0] A と宣言していますけど、これもまぁ、配列みたいなもの。たとえば A=0b0100 とすると、A[2]=1 になる。

9~12 行目が、下位モジュールを接続する記述。

9 行目。FULL_ADDER モジュールを bit0 の全加算器として、インスタンス名 FA0 で接続しています。.A(A[0]) とは、全加算器のポート A に信号 A[0] をいれる、ということ。CI には 0 を入れるので .CI(1’b0) とします。

10 行目。bit1 の CI には、bit0 の CO を接続するので .CI(CO[0])。

そんな感じで、以下同じように。

テストベンチ

前に例題で 4 ビット加算器のシミュレーションをやっています。ほぼ同じです。

- module ADDER_4BIT_TEST;

- reg [3:0] A, B;

- wire [3:0] S;

- wire OF;

- parameter STEP = 10;

- integer i;

- ADDER_4BIT ADDER_4bit(A, B, S, OF);

- initial begin

- A = 4'd0; B= 4'd0;

- for(i=0; i<16; i=i+1) begin

- A = i; B = i % 4; #STEP;

- end

- $finish;

- end

- initial begin

- $dumpfile("adder_4bit_test.vcd");

- $dumpvars(0, ADDER_4BIT_TEST);

- end

- endmodule

14~16 行目の for() 文。ループカウンタ i を 0~15 まで動かしているので、A は 0~15、B は 0~3 の繰返しになります。足し算用の数値サンプル、ってことです。

シミュレーション結果

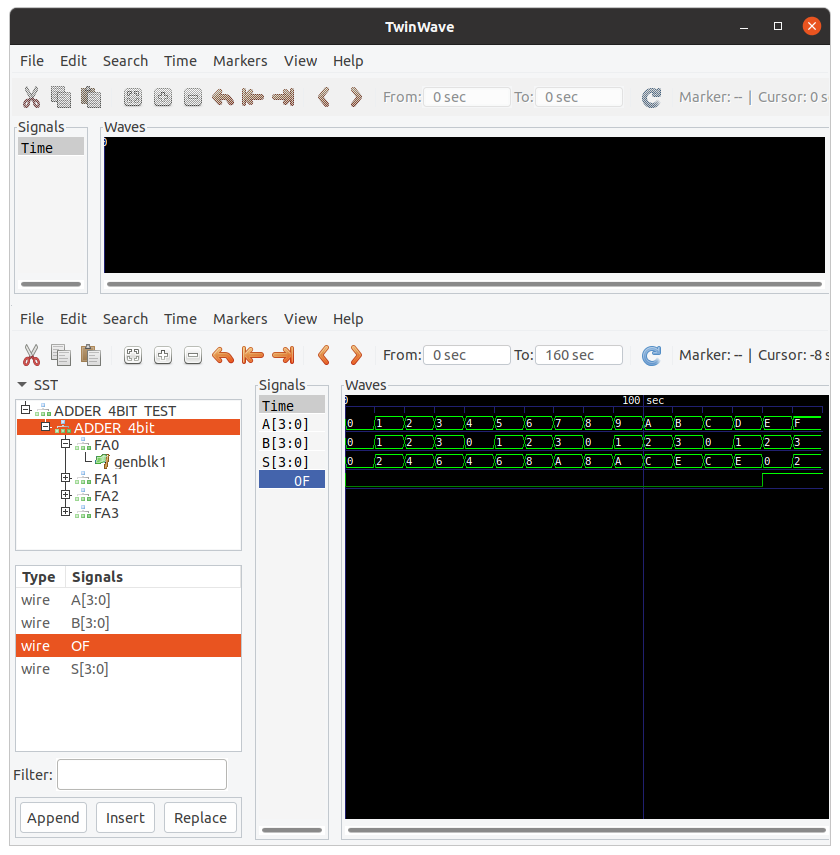

図 2 が、シミュレーション結果です。

ちゃんと加算されています。

ちゃんと加算されています。

うーん、それだけ (^_^;)

あ、値が 16 進数で表示されてます。失礼ですけど、わかります、よね。

後記

シミュレーションやって、うまくいって、はい、できました。では気分が中途半端です。やっぱりじっさいにロジック IC でつくってみて、動かしてみて、ほう、こうなるんだと納得したい (^_^;)

なので、次回は、4 ビット加算器をじっさいに、ロジック IC で組んでみましょう。

論理回路 / 基本的な論理回路

論理回路 / RSフリップフロップ

論理回路 / ゲート型 RS フリップフロップ

論理回路 / プライマリ・レプリカ型 RS フリップフロップ

論理回路 / Dフリップフロップ

論理回路 / JK フリップフロップ

論理回路 / 分周回路・カウンタ回路

論理回路 / 4進同期カウンタ (2bit)

論理回路 / 8進同期カウンタ (3bit)

論理回路 / 16進同期カウンタ (4bit)

論理回路 / 10進同期カウンタと 7セグメントLED

論理回路 / 半加算器と全加算器

論理回路 / 4ビット加算器の構成とシミュレーション

論理回路 / 4ビット加算器をロジック IC でつくる

加算器でカウンタを作る / 構成とシミュレーション

加算器でカウンタを作る / 16進カウンタ

加算器でカウンタをつくる / 10進カウンタ

論理回路 / シフトレジスタ・ジョンソンカウンタ・リングカウンタ

さらに…